側欄

group:architecture

請Archietcture組成員協助編輯

CPU架構設計

研究主題

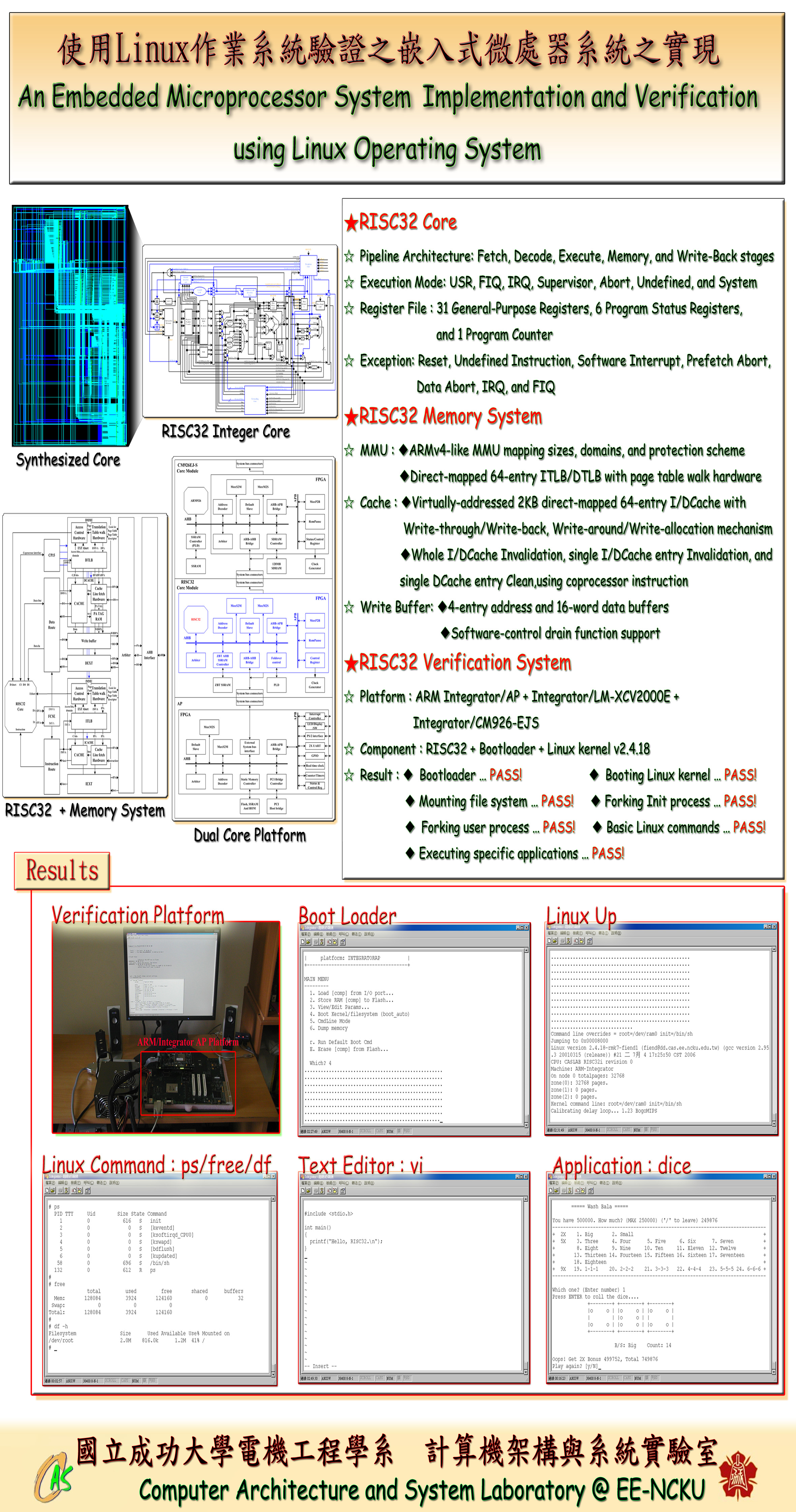

本團隊目前專注於處理器設計相關的議題,包括先進、省電等微架構之研究,相容處理器的實現與嵌入式 OS 印證,Embedded Processor Testing。

團隊成員

現任成員

畢業校友

| 2009年畢業 | (碩) 李宣賢、郭良宇、廖培鈞 |

|---|---|

| 2008年畢業 | (碩) 邱泰恩、吳昱廷 |

| 2007年畢業 | (碩) 吳燈進、李銘峰、許家榮、林奕成 |

| 2006年畢業 | (博) 蕭國樹 (碩) 韋智凱、李哿迦、高洵偉 |

| 2005年畢業 | (碩) 王振傑 |

| 2004年畢業 | (碩) 張哲彰、賴俊福、李易修、王建章、黃富民 |

| 2003年畢業 | (碩) 楊學昌、蔡宜穎、莊武憲 |

| 2002年畢業 | (碩) 柯寧遠 |

| 2001年畢業 | (碩) 蕭國樹 |

研究計畫

執行中的計畫

- 分散式多核心嵌入式原型系統 ─

子計畫(一):多核心處理器暨分散式多核心系統節點平台之設計

Aug. 01, 2007 ~ Jul. 31, 2010 ( 3 years )

- 嵌入式多核心處理器系統軟體開發 ─

多核心處理器晶片軟體測試程式與環境之開發

Aug. 01, 2007 ~ Jul. 31, 2010 ( 3 years )

已結案的計畫

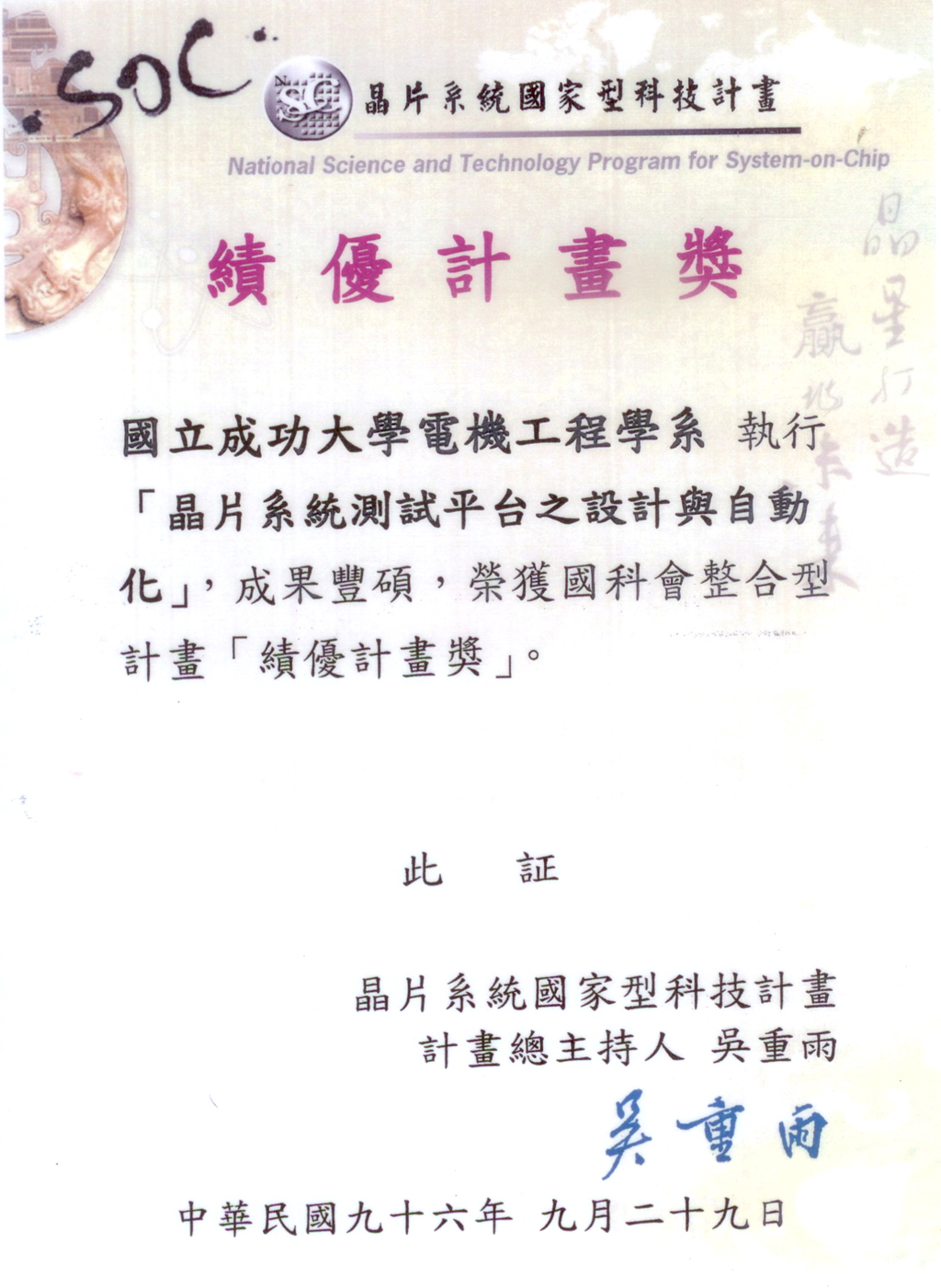

- 晶片系統測試平台之設計與自動化 ─

子計畫(一):適用於SoC測試平台之內嵌式微處理器之設計與測試

Aug. 01, 2004 ~ Jul. 31, 2007 ( 3 years )- 此計畫榮獲國科會整合型計畫『績優計畫獎』

- 一植基於FPGA之多功能積體電路設計驗證平臺

Nov. 01, 2004 ~ Oct. 31, 2005

- 動態二進制轉譯與最佳化之研究

Aug. 01, 2002 ~ Jul. 31, 2003

- 亂序執行處理器之微架構設計及評量

Aug. 01, 1997 ~ Jul. 31, 2000 ( 3 years )

- 建構在VESA Local Bus上之Pentium多處理機系統

Aug. 01, 1995 ~ Jul. 31, 1996

- 建構降低一致尋失率之共享記憶體多處理機

Aug. 01, 1994 ~ Jul. 31, 1995

- 量化分析超純量處理機減少來回計憶體之架構技術

Aug. 01, 1994 ~ Jul. 31, 1995

研究成果

group/architecture.txt · 上一次變更: 2014/11/22 15:05 由 elvis

若無特別註明,本 wiki 上的內容都是採用以下授權方式: CC Attribution-Share Alike 4.0 International