### Chapter 3 Arithmetic for Computers (Part 2)

王振傑 (Chen-Chieh Wang) ccwang@mail.ee.ncku.edu.tw

Computer Organization and Architecture, Fall 2010

## Outline

- 3.3 Multiplication

- 3.4 Division

- 3.5 Floating Point

- 3.9 Concluding Remarks

Department of Electrical Engineering, Feng-Chia University

### **Multiplication**

- More complicated than addition

- accomplished via shifting and addition

- More time and more area

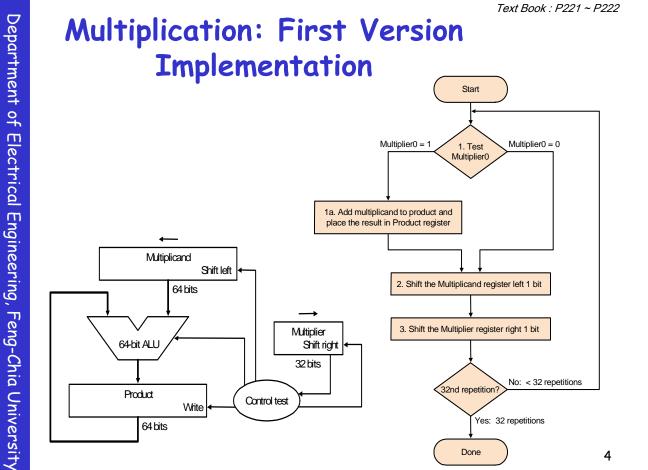

- Let's look at 3 versions based on a gradeschool algorithm

0010 (multiplicand)  $x_1011$  (multiplier)

- See if the right most bit of the multiplier is 1.

- > Shift 1 bit right for the multiplier

- > Note the position of placement Multiplicand is shifted left.

3

Computer Organization and Architecture, Fall 2010

#### EXAMPLE

#### A Multiply Algorithm

Using 4-bit numbers to save space, multiply  $2_{ten} \times 3_{ten}$ , or  $0010_{two} \times 0011_{two}$ .

#### ANSWER

| Iteration | Step                                    | Multiplier | Multiplicand | Product   |

|-----------|-----------------------------------------|------------|--------------|-----------|

| 0         | Initial values                          | 0011       | 0000 0010    | 0000 0000 |

| 1         | 1a: 1 $\Rightarrow$ Prod = Prod + Mcand | 0011       | 0000 0010    | 0000 0010 |

|           | 2: Shift left Multiplicand              | 0011       | 0000 0100    | 0000 0010 |

|           | 3: Shift right Multiplier               | 0001       | 0000 0100    | 0000 0010 |

| 2         | 1a: 1 $\Rightarrow$ Prod = Prod + Mcand | 0001       | 0000 0100    | 0000 0110 |

|           | 2: Shift left Multiplicand              | 0001       | 0000 1000    | 0000 0110 |

|           | 3: Shift right Multiplier               | 0000       | 0000 1000    | 0000 0110 |

| 3         | 1: $0 \Rightarrow$ no operation         | 0000       | 0000 1000    | 0000 0110 |

|           | 2: Shift left Multiplicand              | 0000       | 0001 0000    | 0000 0110 |

|           | 3: Shift right Multiplier               | 0000       | 0001 0000    | 0000 0110 |

| 4         | 1: $0 \Rightarrow$ no operation         | 0000       | 0001 0000    | 0000 0110 |

|           | 2: Shift left Multiplicand              | 0000       | 0010 0000    | 0000 0110 |

|           | 3: Shift right Multiplier               | 0000       | 0010 0000    | 0000 0110 |

5

Computer Organization and Architecture, Fall 2010

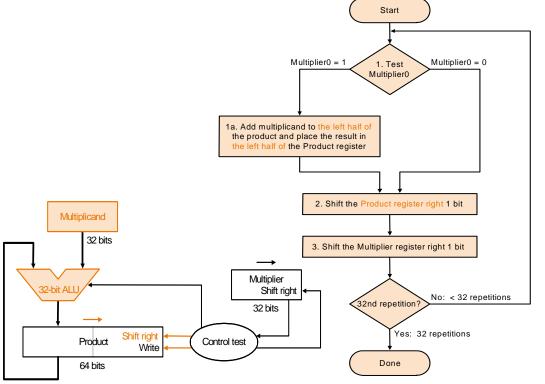

# **Multiplication: Second Version**

Computer Organization and Architecture, Fall 2010

6

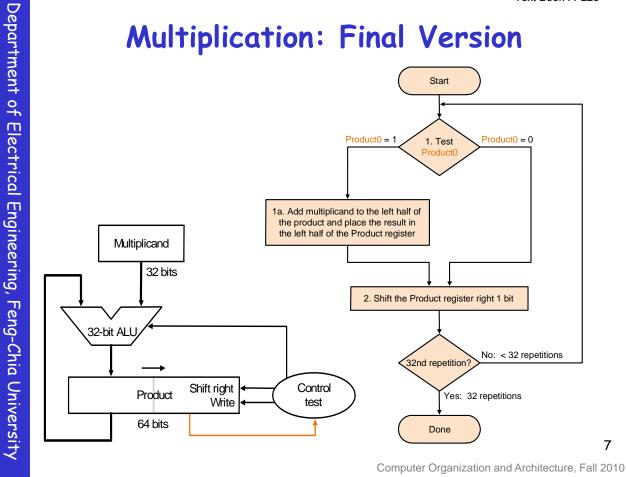

## **Multiplication: Final Version**

Text Book : P225

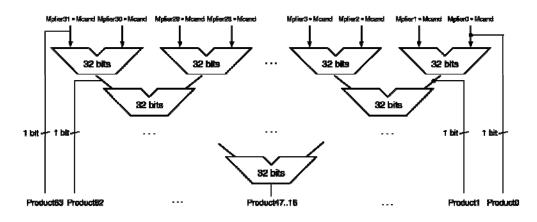

## **Faster Multiplier**

### Uses multiple adders

Cost/performance tradeoff

#### Can be pipelined Several multiplication performed in parallel

8

#### Signed Multiplication : Booth's Algorithm

| x | 0010 <sub>tv</sub><br>0110 <sub>tv</sub> |       |     |    |                   |

|---|------------------------------------------|-------|-----|----|-------------------|

| + | 0000                                     | shift | (0) | in | multiplier)       |

| + | 0010                                     |       |     |    | multiplier)       |

| 1 | 0010                                     | add   |     |    | m. 1+ i = 1 i = ) |

0010 (1 in multiplier) add 0000 shift (0 in multiplier) +

#### 00001100<sub>two</sub>

Booth observed that an ALU that could add or subtract could get the same result in more than one way. For example, since

$$6_{\text{ten}} = -2_{\text{ten}} + 8_{\text{ten}}$$

or

**2 x 6**

0110<sub>two</sub>  $= -0010_{two} + 1000_{two}$

we could replace a string of 1s in the multiplier with an initial subtract when we first see a 1 and then later add when we see the bit after the last 1. For example,

> 0010<sub>two</sub> 0110<sub>two</sub> х 0000 shift (0 in multiplier) + 0010 sub (first 1 in multiplier) + 0000 shift (middle of string of 1s) 0010 add (prior step had last 1) 00001100<sub>two</sub>

9

Computer Organization and Architecture, Fall 2010

#### Booth's Algorithm

| Current bit | Bit to the right | Explanation              | Example                    | aj | <i>a<sub>i-1</sub></i> | Operation  |

|-------------|------------------|--------------------------|----------------------------|----|------------------------|------------|

| 1           | 0                | Beginning of a run of 1s | 00001111000 <sub>two</sub> | 0  | 0                      | Do nothing |

| 1           | 1                | Middle of a run of 1s    | 00001111000 <sub>two</sub> | 0  | 1                      | Add b      |

| 0           | 1                | End of a run of 1s       | 00001111000 <sub>two</sub> | 1  | 0                      | Subtract b |

| 0           | 0                | Middle of a run of Os    | 00001111000 <sub>two</sub> | 1  | 1                      | Do nothing |

- 1. Depending on the current and previous bits, do one of the following:

- 00: Middle of a string of 0s, so no arithmetic operation.

- End of a string of 1s, so add the multiplicand to the left half of the 01:product.

- 10: Beginning of a string of 1s, so subtract the multiplicand from the left half of the product.

- 11: Middle of a string of 1s, so no arithmetic operation.

- 2. As in the previous algorithm, shift the Product register right 1 bit.

Department of Electrical Engineering, Feng-Chia University

10

# Booth's Algorithm Example

#### **⊕** 2 x 6

| Itera-       | Multi- | Original algorith                       | m         | Booth's algorithm                                                 |             |  |

|--------------|--------|-----------------------------------------|-----------|-------------------------------------------------------------------|-------------|--|

| tion plicand |        | Step                                    | Product   | Step                                                              | Product     |  |

| 0            | 0010   | Initial values                          | 0000 0110 | Initial values                                                    | 0000 0110 0 |  |

| 1            | 0010   | 1: 0 $\rightarrow$ no operation         | 0000 0110 | 1a: 00 $\rightarrow$ no operation                                 | 0000 0110 0 |  |

|              | 0010   | 2: Shift right Product                  | 0000 0011 | 2: Shift right Product                                            | 0000 0011 0 |  |

| 2            | 0010   | 1a: 1 $\implies$ Prod = Prod + Mcand    | 0010 0011 | 1c: $10 \Longrightarrow \text{Prod} = \text{Prod} - \text{Mcand}$ | 1110 0011 0 |  |

|              | 0010   | 2: Shift right Product                  | 0001 0001 | 2: Shift right Product                                            | 1111 0001 1 |  |

| 3            | 0010   | 1a: 1 $\Rightarrow$ Prod = Prod + Mcand | 0011 0001 | 1d: 11 $\Rightarrow$ no operation                                 | 1111 0001 1 |  |

|              | 0010   | 2: Shift right Product                  | 0001 1000 | 2: Shift right Product                                            | 1111 1000 1 |  |

| 4            | 0010   | 1: $0 \Rightarrow$ no operation         | 0001 1000 | 1b: $01 \implies \text{Prod} = \text{Prod} + \text{Mcand}$        | 0001 1000 1 |  |

|              | 0010   | 2: Shift right Product                  | 0000 1100 | 2: Shift right Product                                            | 0000 1100 0 |  |

11 Computer Organization and Architecture, Fall 2010

# Booth's Algorithm Example

#### **Booth's Algorithm**

Let's try Booth's algorithm with negative numbers:  $2_{\text{ten}} \times -3_{\text{ten}} = -6_{\text{ten}}$ , or  $0010_{\text{two}} \times 1101_{\text{two}} = 1111\ 1010_{\text{two}}$ .

| Iteration              | Step                                         | Multiplicand | Product            |

|------------------------|----------------------------------------------|--------------|--------------------|

| 0                      | Initial values                               | 0010         | 0000 1101 0        |

| 1                      | 1c: $10 \Longrightarrow Prod = Prod - Mcand$ | 0010         | 1110 1101 0        |

|                        | 2: Shift right Product                       |              | 1111 0110 1        |

| 2                      | 1b: $01 \Longrightarrow Prod = Prod + Mcand$ | 0010         | 0001 0110 1        |

|                        | 2: Shift right Product                       | 0010         | 0000 1011 0        |

| 3                      | 1c: 10 $\implies$ Prod = Prod - Mcand        | 0010         | 1110 1011 0        |

| 2: Shift right Product |                                              | 0010         | 1111 0101 <b>1</b> |

| 4                      | 4 1d: 11 $\Rightarrow$ no operation          |              | 1111 0101 1        |

|                        | 2: Shift right Product                       | 0010         | 1111 1010 <b>1</b> |

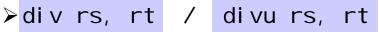

# **MIPS Multiplication**

#### Two 32-bit registers for product

- > HI: most-significant 32 bits

- LO: least-significant 32-bits

#### Instructions

- ▶ mult rs, rt multu rs, rt /

- 64-bit product in HI/LO

- ▶ mfhi rd / mflo rd

- Move from HI/LO to rd

- Can test HI value to see if product overflows 32 bits

#### ▶ mul rd, rs, rt

• Least-significant 32 bits of product -> rd

13 Computer Organization and Architecture, Fall 2010

## Outline

- **Multiplication** 3.3

- 3.4 Division

- **Floating Point** 3.5

- **Concluding Remarks** 3.9

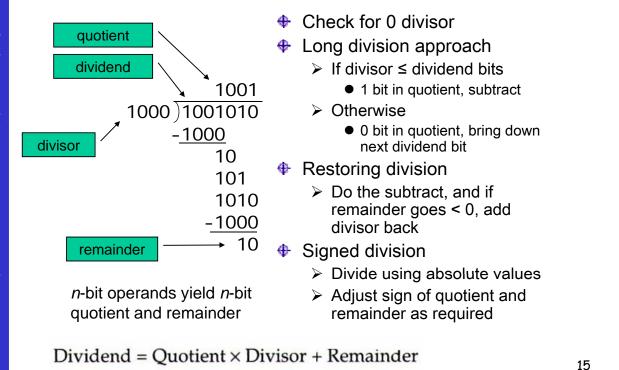

#### Division

Computer Organization and Architecture, Fall 2010

# **MIPS** Division

- Use HI/LO registers for result

- ➢ HI: 32-bit remainder

- ≻ LO: 32-bit quotient

#### Instructions

- No overflow or divide-by-0 checking

- Software must perform checks if required

- Use mfhi, mfl o to access result

# Outline

- **Multiplication** 3.3

- 3.4 Division

- 3.5 Floating Point

- **Concluding Remarks** 3.9

17 Computer Organization and Architecture, Fall 2010

Text Book : P232

# Floating Point (a brief look)

- We need a way to represent

- > numbers with fractions, e.g., 3.14159265... (pi)

- very small numbers, e.g., 0.000000001 = 1.0 x 10 -9

- very large numbers, e.g., 3,155,760,000 = 3.15576 x 10 <sup>9</sup>

#### Representation:

- > sign, exponent, significand:  $(-1)^{\text{sign}} \times \text{significand} \times 2^{\text{exponent}}$

- more bits for significand gives more accuracy

- more bits for exponent increases range

## **IEEE 754 floating-point standard**

#### Single precision : 8 bit exponent, 23 bit significand

| S     | Exponent | significand |

|-------|----------|-------------|

| 1 bit | 8 bits   | 23 bits     |

#### Double precision : 11 bit exponent, 52 bit significand

| S       | Exponent | significand ~ |  |  |  |

|---------|----------|---------------|--|--|--|

| 1 bit   | 11 bits  | 20 bits       |  |  |  |

|         |          | ~ significand |  |  |  |

| 32 bits |          |               |  |  |  |

- Leading "1" bit of significand is implicit

- Exponent is "biased" to make sorting easier

- > all 0s is smallest exponent all 1s is largest

- bias of 127 for single precision and 1023 for double precision

- ➤ summary: (-1)<sup>sign</sup> x (1+significand) x 2<sup>exponent bias</sup>

#### 19

Computer Organization and Architecture, Fall 2010

Text Book : P236 ~ P237

# **IEEE 754 floating-point standard**

#### Example:

- $\blacktriangleright$  decimal: 0.75 = ( $\frac{1}{2} + \frac{1}{4}$ )

- ➢ binary: 0.11 = -1.1 x 2<sup>-1</sup>

- $\blacktriangleright$  floating point: exponent = 126 = 01111110 (after add 127)

#### > IEEE single precision:

| 1     | 01111110 | 100000000000000000000000000000000000000 |

|-------|----------|-----------------------------------------|

| 1 bit | 8 bits   | 23 bits                                 |

Department of Electrical Engineering, Feng-Chia University

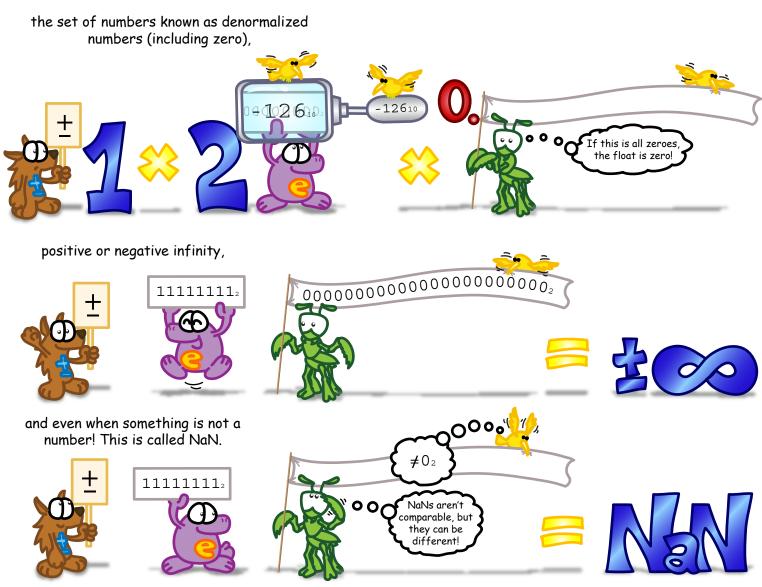

### **IEEE 754 Encoding**

| Single precision |          | Double precision |          | Object represented      |

|------------------|----------|------------------|----------|-------------------------|

| Exponent         | Fraction | Exponent         | Fraction |                         |

| 0                | 0        | 0                | 0        | 0                       |

| 0                | nonzero  | 0                | nonzero  | ± denormalized number   |

| 1-254            | anything | 1-2046           | anything | ± floating-point number |

| 255              | 0        | 2047             | 0        | ± infinity              |

| 255              | nonzero  | 2047             | nonzero  | NaN (Not a Number)      |

| S     | Exponent | significand |

|-------|----------|-------------|

| 1 bit | 8 bits   | 23 bits     |

21 Computer Organization and Architecture, Fall 2010

Text Book : P235

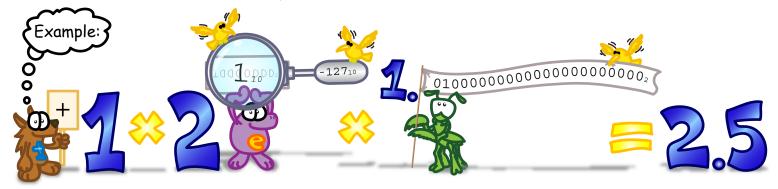

## **Denormalized Numbers**

$\oplus$  Exponent = 000...0  $\Rightarrow$  hidden bit is 0

$$x = (-1)^{s} \times (0 + Fraction) \times 2^{-Bias}$$

Smaller than normal numbers

allow for gradual underflow, with diminishing precision

Denormal with fraction = 000...0

$$x = (-1)^{s} \times (0+0) \times 2^{-Bias} = \pm 0.0$$

Two representations of 0.0!

### **Infinities and NaNs**

Exponent = 111...1, Fraction = 000...0

➤ ±Infinity

Can be used in subsequent calculations, avoiding need for overflow check

####

- Not-a-Number (NaN)

- Indicates illegal or undefined result

- e.g., 0.0 / 0.0

- Can be used in subsequent calculations

23 Computer Organization and Architecture, Fall 2010

## IEEE 754 floating-point (32-bit)

| A Massimum                              |                                | 1111110                                              | 111111111111111111111111                |  |  |  |

|-----------------------------------------|--------------------------------|------------------------------------------------------|-----------------------------------------|--|--|--|

| 💠 Maximum                               | 0                              | 1111110                                              |                                         |  |  |  |

|                                         | 1 bit                          | 8 bits                                               | 23 bits                                 |  |  |  |

|                                         | 000000<br>- 2 <sup>(-23)</sup> | 11111111111<br>000000000000<br>x 2 <sup>(+127)</sup> |                                         |  |  |  |

| 🚸 Minimum                               | 0                              | 0000000                                              | 000000000000000000000000000000000000000 |  |  |  |

|                                         | 1 bit                          | 8 bits                                               | 23 bits                                 |  |  |  |

| = 0.00000000000000000000000000000000000 |                                |                                                      |                                         |  |  |  |

Department of Electrical Engineering, Feng-Chia University

Text Book : P243

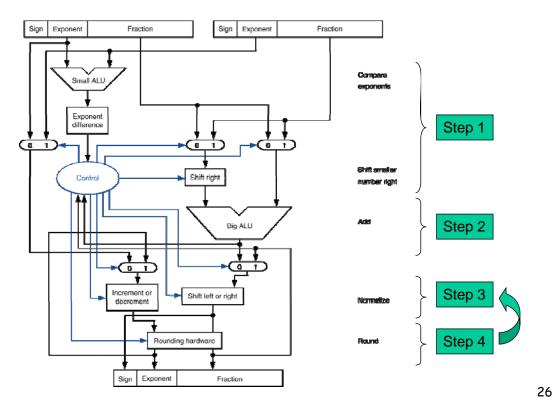

### **FP** Adder Hardware

Computer Organization and Architecture, Fall 2010

# **FP Instructions in MIPS**

- FP hardware is coprocessor 1

- > Adjunct processor that extends the ISA

- Separate FP registers

- > 32 single-precision: \$f0, \$f1, ... \$f31

- Paired for double-precision: \$f0/\$f1, \$f2/\$f3, ...

- Release 2 of MIPs ISA supports 32 × 64-bit FP reg's

- FP instructions operate only on FP registers

- Programs generally don't do integer ops on FP data, or vice versa

- More registers with minimal code-size impact

- FP load and store instructions

- I wc1, I dc1, swc1, sdc1

- e.g., I dc1 \$f8, 32(\$sp)

### **FP Instructions in MIPS**

Single-precision arithmetic

add. s, sub. s, mul. s, div.s

e.g., add. s \$f0, \$f1, \$f6

Double-precision arithmetic

add. d, sub. d, mul. d, di v. d

e.g., mul. d \$f4, \$f4, \$f6

Single- and double-precision comparison

c. xx. s, c. xx. d (xx is eq, l t, l e, ...)

Sets or clears FP condition-code bit

e.g. c. l t. s \$f3, \$f4

Branch on FP condition code true or false

bc1t, bc1f

e.g., bc1t TargetLabel

29 Computer Organization and Architecture, Fall 2010

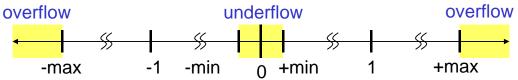

## **Floating Point Complexities**

- Operations are somewhat more complicated (see text)

- In addition to overflow we can have "underflow"

- Accuracy can be a big problem

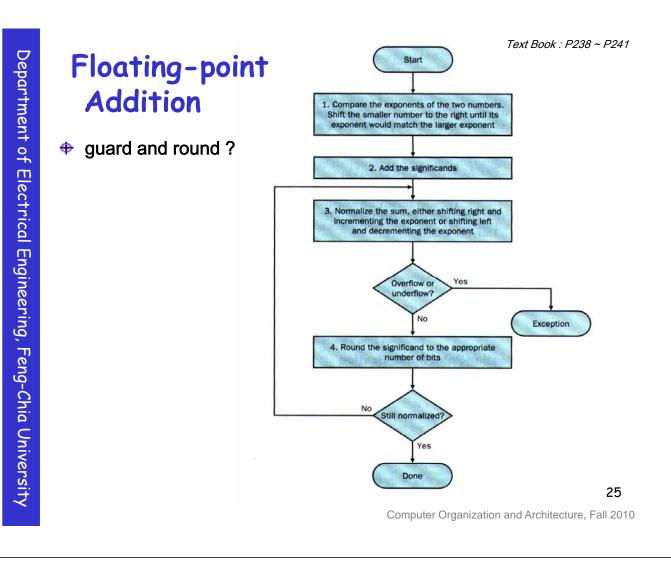

- IEEE 754 keeps two extra bits, guard and round

- four rounding modes

- > positive divided by zero yields "infinity"

- > zero divide by zero yields "not a number"

- > other complexities

- Implementing the standard can be tricky

- Not using the standard can be even worse

- > see text for description of 80x86 and Pentium bug!

# Outline

- 3.3 Multiplication

- 3.4 Division

- 3.5 Floating Point

- 3.9 Concluding Remarks

31 Computer Organization and Architecture, Fall 2010

Department of Electrical Engineering, Feng-Chia University

### Summary

- Computer arithmetic is constrained by limited precision

- Bit patterns have no inherent meaning but standards do exist

- ➤ two's complement

- IEEE 754 floating point

- Computer instructions determine "meaning" of the bit patterns

- Performance and accuracy are important so there are many complexities in real machines

- Algorithm choice is important and may lead to hardware optimizations for both space and time (e.g., multiplication)

#### In More Depth: Booth's Algorithm

A more elegant approach to multiplying signed numbers than above is called *Booth's algorithm*. It starts with the observation that with the ability to both add and subtract there are multiple ways to compute a product. Suppose we want to multiply  $2_{\text{ten}}$  by  $6_{\text{ten}}$ , or  $0010_{\text{two}}$  by  $0110_{\text{two}}$ :

```

\begin{array}{r} & 0010_{two} \\ x & 0110_{two} \\ + & 0000 \text{ shift (0 in multiplier)} \\ + & 0010 \text{ add (1 in multiplier)} \\ + & 0010 \text{ add (1 in multiplier)} \\ + & 0000 \text{ shift (0 in multiplier)} \\ \hline & 00001100_{two} \end{array}

```

Booth observed that an ALU that could add or subtract could get the same result in more than one way. For example, since

$$6_{\text{ten}} = - 2_{\text{ten}} + 8_{\text{ten}}$$

or

$0110_{two} = - 0010_{two} + 1000_{two}$

we could replace a string of 1s in the multiplier with an initial subtract when we first see a 1 and then later add when we see the bit *after* the last 1. For example,

```

0010two

x 0110two

+ 0000 shift (0 in multiplier)

- 0010 sub (first 1 in multiplier)

+ 0000 shift (middle of string of 1s)

+0010 add (prior step had last 1)

00001100two

```

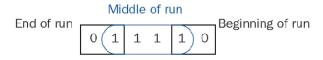

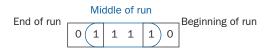

Booth invented this approach in a quest for speed because in machines of his era shifting was faster than addition. Indeed, for some patterns his algorithm would be faster; it's our good fortune that it handles signed numbers as well, and we'll prove this later. The key to Booth's insight is in his classifying groups of bits into the beginning, the middle, or the end of a run of 1s:

Of course, a string of 0s already avoids arithmetic, so we can leave these alone.

If we are limited to looking at just 2 bits, we can then try to match the situation in the preceding drawing, according to the value of these 2 bits:

If we are limited to looking at just 2 bits, we can then try to match the situation in the preceding drawing, according to the value of these 2 bits:

| Current bit | Bit to the right | Explanation              | Example                                   |

|-------------|------------------|--------------------------|-------------------------------------------|

| 1           | 0                | Beginning of a run of 1s | 00001111000 <sub>two</sub>                |

| 1           | 1                | Middle of a run of 1s    | 00001111000 <sub>two</sub>                |

| 0           | 1                | End of a run of 1s       | 000 <mark>01</mark> 111000 <sub>two</sub> |

| 0           | 0                | Middle of a run of Os    | 00001111000 <sub>two</sub>                |

Booth's algorithm changes the first step of the algorithm—looking at 1 bit of the multiplier and then deciding whether to add the multiplicand—to looking at 2 bits of the multiplier. The new first step, then, has four cases, depending on the values of the 2 bits. Let's assume that the pair of bits examined consists of the current bit and the bit to the right—which was the current bit in the previous step. The second step is still to shift the product right. The new algorithm is then the following:

- 1. Depending on the current and previous bits, do one of the following:

- 00: Middle of a string of 0s, so no arithmetic operation.

- 01: End of a string of 1s, so add the multiplicand to the left half of the product.

- 10: Beginning of a string of 1s, so subtract the multiplicand from the left half of the product.

- 11: Middle of a string of 1s, so no arithmetic operation.

- 2. As in the previous algorithm, shift the Product register right 1 bit.

Now we are ready to begin the operation, shown in Figure 3.11.2. It starts with a 0 for the mythical bit to the right of the rightmost bit for the first stage. Figure 3.11.2 compares the two algorithms, with Booth's on the right. Note that Booth's operation is now identified according to the values in the 2 bits. By the fourth step, the two algorithms have the same values in the Product register.

The one other requirement is that shifting the product right must preserve the sign of the intermediate result, since we are dealing with signed numbers. The solution is to extend the sign when the product is shifted to the right. Thus, step 2 of the second iteration turns 1110 0011  $0_{two}$  into 1111 0001  $1_{two}$  instead of 0111 0001  $1_{two}$ . This shift is called an *arithmetic right shift* to differentiate it from a logical right shift.

| Itera- | Multi-<br>plicand | Original algorithm                                      |           | Booth's algorithm                     |             |

|--------|-------------------|---------------------------------------------------------|-----------|---------------------------------------|-------------|

| tion   |                   | Step                                                    | Product   | Step                                  | Product     |

| 0      | 0010              | Initial values 0000 0110 Initial values                 |           | 0000 0110 0                           |             |

| 1      | 0010              | 1: 0 $\Rightarrow$ no operation                         | 0000 0110 | 1a: 00 $\Rightarrow$ no operation     | 0000 0110 0 |

|        | 0010              | 2: Shift right Product 0000 0011 2: Shift right Product |           | 0000 0011 0                           |             |

| 2      | 0010              | 1a: 1 $\implies$ Prod = Prod + Mcand                    | 0010 0011 | 1c: 10 $\implies$ Prod = Prod - Mcand | 1110 0011 0 |

|        | 0010              | 2: Shift right Product                                  | 0001 0001 | 2: Shift right Product                | 1111 0001 1 |

| 3      | 0010              | 1a: 1 $\Rightarrow$ Prod = Prod + Mcand                 | 0011 0001 | 1d: 11 $\Rightarrow$ no operation     | 1111 0001 1 |

|        | 0010              | 2: Shift right Product                                  | 0001 1000 | 2: Shift right Product                | 1111 1000 1 |

| 4      | 0010              | 1: 0 $\Rightarrow$ no operation                         | 0001 1000 | 1b: 01 $\implies$ Prod = Prod + Mcand | 0001 1000 1 |

|        | 0010              | 2: Shift right Product                                  | 0000 1100 | 2: Shift right Product                | 0000 1100 0 |

**FIGURE 3.11.2** Comparing algorithm in Booth's algorithm for positive numbers. The bit(s) examined to determine the next step is circled in color.

#### **Booth's Algorithm**

Let's try Booth's algorithm with negative numbers:  $2_{ten} \times -3_{ten} = -6_{ten}$ , or  $0010_{two} \times 1101_{two} = 1111\ 1010_{two}$ .

#### **EXAMPLE**

Figure 3.11.3 shows the steps.

#### ANSWER

| Iteration | Step                                                       | Multiplicand | Product     |

|-----------|------------------------------------------------------------|--------------|-------------|

| 0         | Initial values                                             | 0010         | 0000 1101 0 |

| 1         | 1c: $10 \implies \text{Prod} = \text{Prod} - \text{Mcand}$ | 0010         | 1110 1101 0 |

|           | 2: Shift right Product                                     | 0010         | 1111 0110 1 |

| 2         | 1b: $01 \implies \text{Prod} = \text{Prod} + \text{Mcand}$ | 0010         | 0001 0110 1 |

|           | 2: Shift right Product                                     | 0010         | 0000 1011 0 |

| 3         | 1c: $10 \implies Prod = Prod - Mcand$                      | 0010         | 1110 1011 0 |

|           | 2: Shift right Product                                     | 0010         | 1111 0101 1 |

| 4         | 1d: 11 $\Rightarrow$ no operation                          | 0010         | 1111 0101 1 |

|           | 2: Shift right Product                                     | 0010         | 1111 1010 1 |

**FIGURE 3.11.3 Booth's algorithm with negative multiplier example.** The bits examined to determine the next step are circled in color.

Our example multiplies one bit at a time, but it is possible to generalize Booth's algorithm to generate multiple bits for faster multiplies (see Exercise 3.50)

Now that we have seen Booth's algorithm work, we are ready to see *why* it works for two's complement signed integers. Let *a* be the multiplier and *b* be the multiplicand and we'll use  $a_i$  to refer to bit *i* of *a*. Recasting Booth's algorithm in terms of the bit values of the multiplier yields this table:

| a <sub>i</sub> | a <sub>i-1</sub> | Operation  |

|----------------|------------------|------------|

| 0              | 0                | Do nothing |

| 0              | 1                | Add b      |

| 1              | 0                | Subtract b |

| 1              | 1                | Do nothing |

Instead of representing Booth's algorithm in tabular form, we can represent it as the expression

$(a_{i-1} - a_i)$

where the value of the expression means the following actions:

- 0: do nothing +1: add b

- -1: subtract *b*

Since we know that shifting of the multiplicand left with respect to the Product register can be considered multiplying by a power of 2, Booth's algorithm can be written as the sum

$(a_{-1} - a_0) \times b \times 2^0$  $+ (a_0 - a_1) \times b \times 2^1$  $+ (a_1 - a_2) \times b \times 2^2$  $\cdots$  $+ (a_{29} - a_{30}) \times b \times 2^{30}$  $+ (a_{30} - a_{31}) \times b \times 2^{31}$

We can simplify this sum by noting that

$$-a_i \times 2^i + a_i \times 2^{i+1} = (-a_i + 2a_i) \times 2^i = (2a_i - a_i) \times 2^i = a_i \times 2^i$$

recalling that  $a_{-1} = 0$  and by factoring out *b* from each term:

$b \times ((a_{31} \times -2^{31}) + (a_{30} \times 2^{30}) + (a_{29} \times 2^{29}) + \ldots + (a_1 \times 2^1) + (a_0 \times 2^0))$

The long formula in parentheses to the right of the first multiply operation is simply the two's complement representation of a (see page 163). Thus, the sum is further simplified to

$b \times a$

Hence, Booth's algorithm does in fact perform two's complement multiplication of *a* and *b*.

**3.23** [30] < 3.6> The original reason for Booth's algorithm was to reduce the number of operations by avoiding operations when there were strings of 0s and 1s. Revise the algorithm on page IMD 3.11-2 to look at 3 bits at a time and compute the product 2 bits at a time. Fill in the following table to determine the 2-bit Booth encoding:

| Current bits |    | Previous bit  | Operation | Reason |

|--------------|----|---------------|-----------|--------|

| a <i>i+1</i> | ai | a <i>i</i> –1 |           |        |

| 0            | 0  | 0             |           |        |

| 0            | 0  | 1             |           |        |

| 0            | 1  | 0             |           |        |

| 0            | 1  | 1             |           |        |

| 1            | 0  | 0             |           |        |

| 1            | 0  | 1             |           |        |

| 1            | 1  | 0             |           |        |

| 1            | 1  | 1             |           |        |

Assume that you have both the multiplicand and  $2 \times$  multiplicand already in registers. Explain the reason for the operation on each line, and show a 6-bit example that runs faster using this algorithm. (Hint: Try dividing to conquer; see what the operations would be in each of the eight cases in the table using a 2-bit Booth algorithm, and then optimize the pair of operations.)

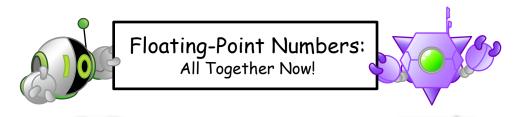

An IEEE 754 floating point number consists of three parts:

the Exponent,

and the Mantissa.

(Also known as the Significand)

10000002

.141592

The Sign, as its name suggests, determines the sign of the number.

The Exponent plays a vital role in determining how big (or small) the number is. However, it's encoded so that unsigned comparison can be used to check floating-point numbers.

-12710

To see the true magnitude of the Exponent, you'd need to subtract the Bias, a special number determined by the length of the Exponent.

> And last but not least, the Mantissa holds the significant digits of the floating point number.

Once all the parts of the floating-point number are obtained, converting it to decimal is just a matter of applying the following formula:

Notice that the Mantissa actually represents a fraction, instead of an integer! In addition to representing real numbers, the IEEE 754 representation can also indicate...

Ketrina Yim

Due to the format of the IEEE-754 standard, the floating-point numbers can be plotted on a number line. In fact, the floating-point numbers are arranged so that they can be incremented like a binary odometer!

Ketrina fim