# 邏輯系統設計實驗 課程大綱

Department of Electrical Engineering National Cheng Kung University

#### 實驗課目的

- •練習以 IC 實現電路

- · 學習 verilog 並且進行電路模擬

- 利用 verilog 在 FPGA 上部屬自己的電路與應用

# 實驗課周次

- 使用 IC 進行數位邏輯電路設計

- 2/21 基本邏輯閘實作

- 3/7 Decoder/Encoder/Mux/Demux

- 3/14 加法器

- 學習 verilog 並且進行電路模擬

- 3/21 Vivado 環境與 Verilog 簡介

- 3/28 Combinational 電路

- 4/4 校際活動週

- 4/11 期中週放假

- 4/18 Sequantial 電路 (1)

- 4/25 Sequantial 電路 (2)

- 5/2 Sequantial 電路 (3)

### 實驗課周次 (續)

- 利用 verilog 在 FPGA 上部屬自己的電路與應用

- 5/9

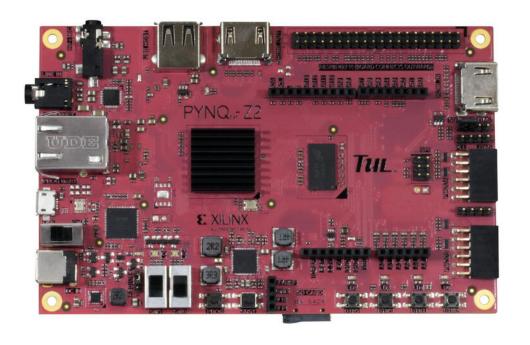

- /9 Pynq 與 7 段顯示器

- 5/16

- 紅綠燈與 PWM 呼吸燈

• 5/23~6/13

- Final Project

#### 結報繳交

• 在截止當天 23:59 繳交至 moodle ,遲交一週將以 70% 分數計算。

• 如果有課程問題,可以以 [LogicLab23] 作為主旨開頭寄信至 course@caslab.ee.ncku.edu.tw ,以便助教檢視。

#### 評分標準

• 60% 實驗結報內容 (10 次實驗)

• 10% 上課參與度

• 30% Final Project

# 實驗課注意事項

- 每週實驗課內容以及重要通知都會放在實驗課網站 https://caslab.ee.ncku.edu.tw/dokuwiki/course:logic \_system\_practice:111 上

- 每週記得簽到,到課次數會影響上課參與度分數

- 完成時候後記得請助教進行檢查,並且做好紀錄以便 結報時使用,是否有請助教檢查完成也會影響上課參 與度分數

- 實驗室嚴禁飲食,違規者扣總分10分

# 此次實驗課需要完成事項

- 受限於實驗課器材,因此需要分組進行實驗

- 2~3 人為一組

- 當天沒有完成分組的人會由助教分組