#### Lecture 9 Multiplexer, Decoder, and PLD

- SSI (small-scale integration)

NAND, NOR, NOT, flip flop etc

- Gate count < 10.

- MSI (medium-scale integration)

- Adders, multiplexers, decoders, registers, counters

- Gate count < 100

- LSI

- VLSI (very large-scale integration

Memory chips, microprocessors

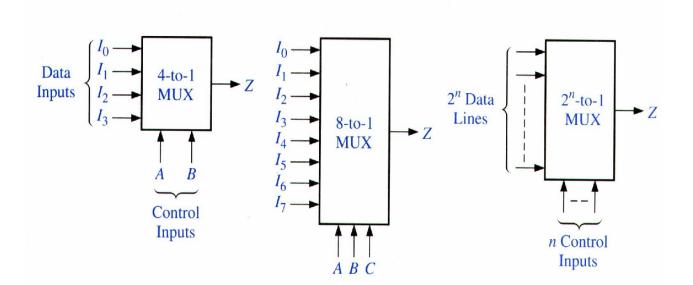

#### Multiplexers

Multiplexers are selectors.

Z = A'B'I<sub>0</sub> + A'BI<sub>1</sub> + AB'I<sub>2</sub> + ABI<sub>3</sub>. (4-to-1 MUX)

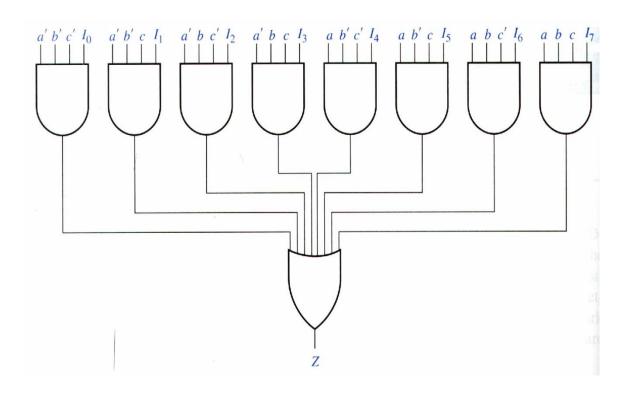

#### Logic Diagram for MUX

#### • 8-to-1 MUX

#### Application of MUX

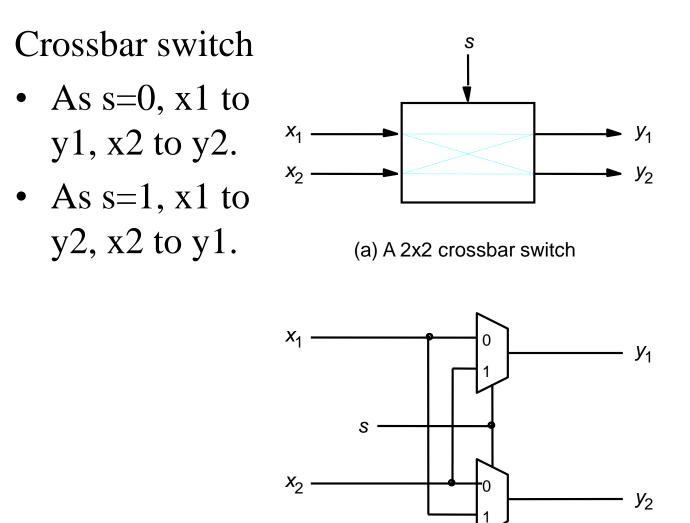

• Select data.

#### Application of MUX

(b) Implementation using multiplexers

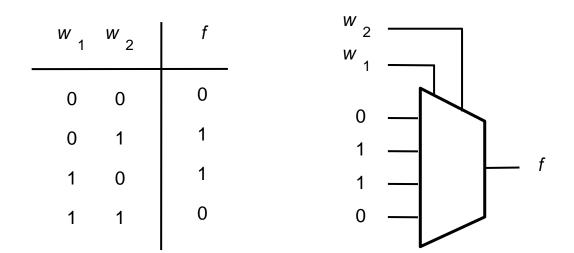

#### Using Mux for logic function, XOR

•  $f = w_1 \text{ xor } w_2$

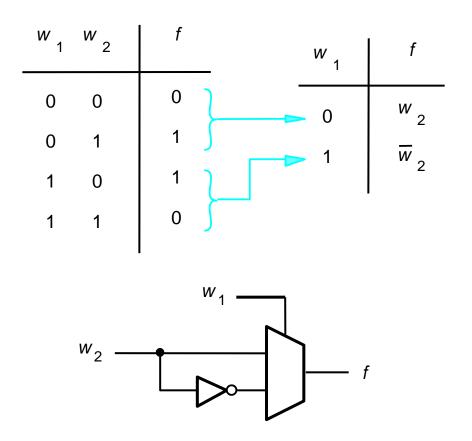

#### Better

- Modify the truth table.

- When  $w_1 = 0$ ,  $f = w_2$ . Otherwise,  $f = \sim w_2$

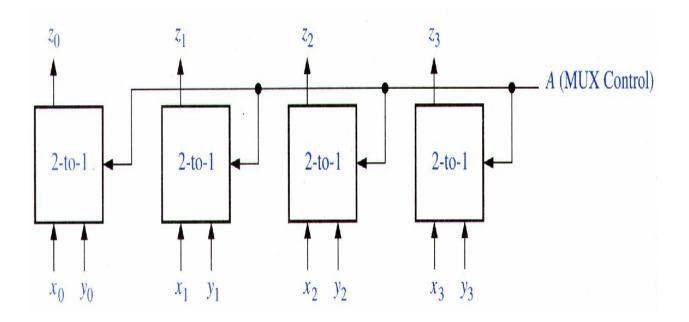

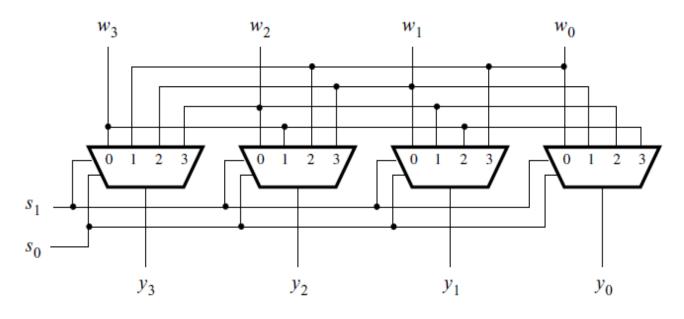

#### Using Mux to Implement a barrel shifter

| $s_1$ | <i>s</i> <sub>0</sub> | $y_3$                 | $y_2$                 | $y_1$ | $y_0$ |

|-------|-----------------------|-----------------------|-----------------------|-------|-------|

| 0     | 0                     | <i>w</i> <sub>3</sub> | <i>w</i> <sub>2</sub> | $w_1$ | $w_0$ |

| 0     | 1                     | w <sub>0</sub>        | $w_3$                 | $w_2$ | $w_1$ |

| 1     | 0                     | $w_1$                 | $w_0$                 | $w_3$ | $w_2$ |

| 1     | 1                     | <i>w</i> <sub>2</sub> | $w_1$                 | $w_0$ | $w_3$ |

#### (a) Truth table

(b) Circuit

Chap 9

C-H 8

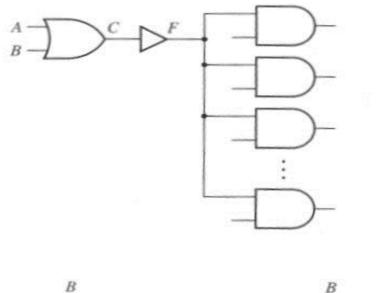

#### Buffers/Tri-state Buffer

- Driving capability

- High impedance

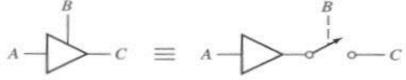

## Tri-state Buffer Application

• Data transfer between registers

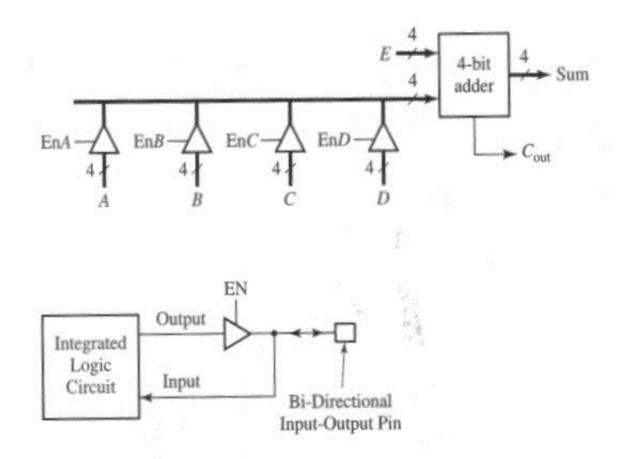

# Tri-state Buffer Application (cont.)

Source selection

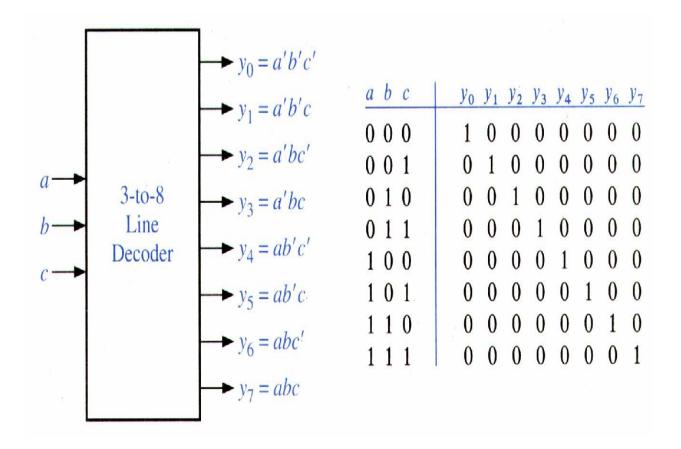

#### Decoder

- 3-to-8 line decoder

- An n-to-2<sup>n</sup> decoder generates all 2<sup>n</sup> minterms of the n input variables.

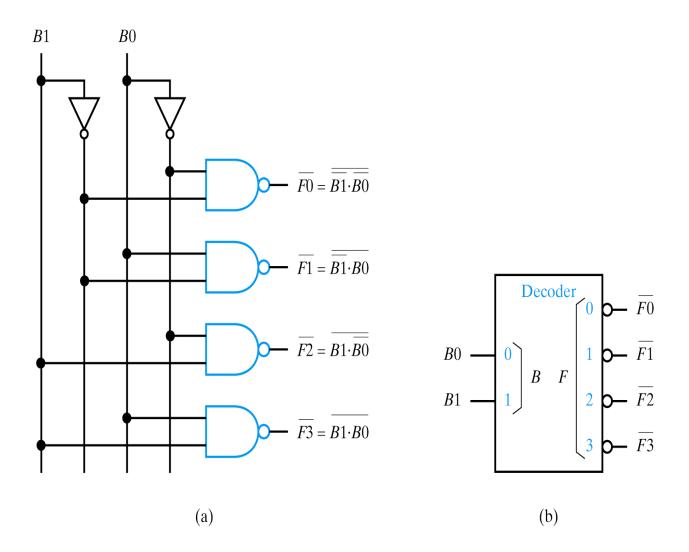

#### More Decoder

• 2-to-4 decoder: minterm generator

Figure 3.5.3 Decoder: (a) gate-level circuit diagram, (b) logic symbol.

#### Decoder (cont.)

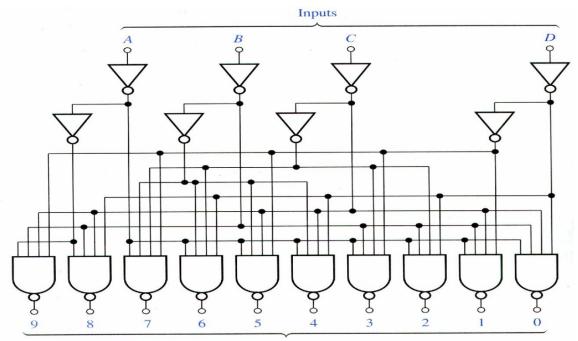

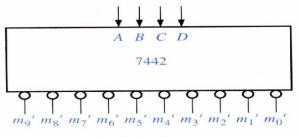

• 4-to-10 line decoder

Outputs

(a) Logic diagram

(b) Block diagram

| BCD Input | Decimal Output        |

|-----------|-----------------------|

| ABCD      | 0 1 2 3 4 5 6 7 8 9   |

| 0 0 0 0   | 0 1 1 1 1 1 1 1 1 1   |

| 0 0 0 1   | 1011111111            |

| 0 0 1 0   | 1 1 0 1 1 1 1 1 1 1   |

| 0 0 1 1   | 1 1 1 0 1 1 1 1 1 1   |

| 0 1 0 0   | 1 1 1 1 0 1 1 1 1 1   |

| 0 1 0 1   | 1 1 1 1 1 0 1 1 1 1   |

| 0 1 1 0   | 1 1 1 1 1 1 0 1 1 1   |

| 0 1 1 1   | 1 1 1 1 1 1 1 0 1 1   |

| 1 0 0 0   | 1 1 1 1 1 1 1 1 0 1   |

| 1 0 0 1   | 1 1 1 1 1 1 1 1 1 0   |

| 1 0 1 0   | 1 1 1 1 1 1 1 1 1 1 1 |

| 1 0 1 1   | 1 1 1 1 1 1 1 1 1 1 1 |

| 1 1 0 0   | 1 1 1 1 1 1 1 1 1 1 1 |

| 1 1 0 1   | 1 1 1 1 1 1 1 1 1 1 1 |

| 1 1 1 0   | 1 1 1 1 1 1 1 1 1 1 1 |

| 1 1 1 1   | 1 1 1 1 1 1 1 1 1 1 1 |

(c) Truth table

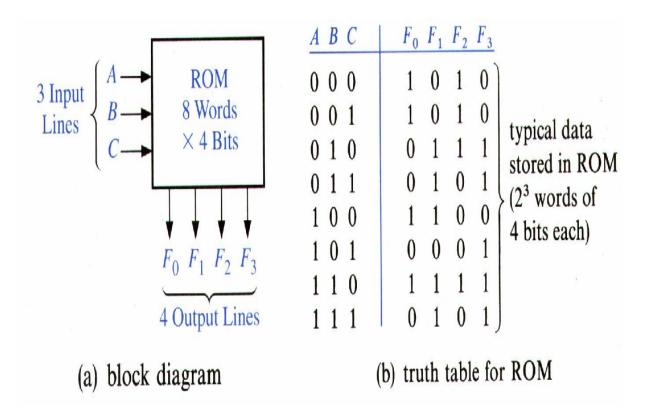

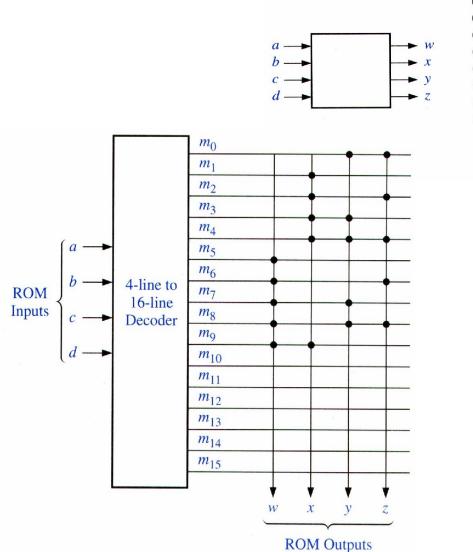

# ROM

• Read-only memory: stored data can not be changed under normal operating conditions.

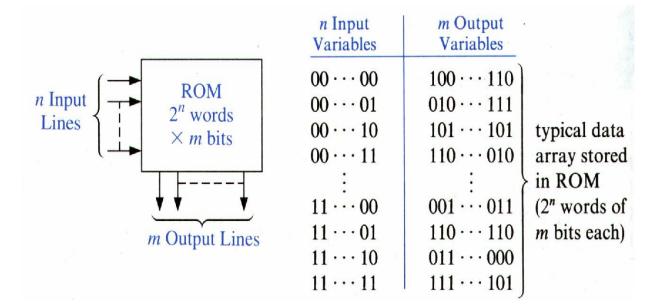

# ROM (cont.)

• ROM size =  $2^n \times m$  bits.

Chap 9

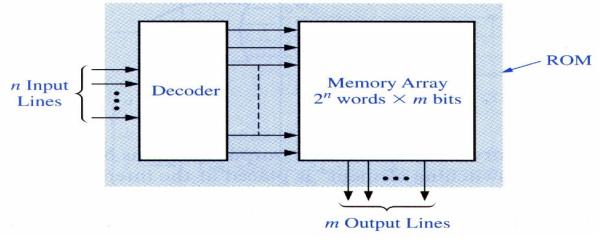

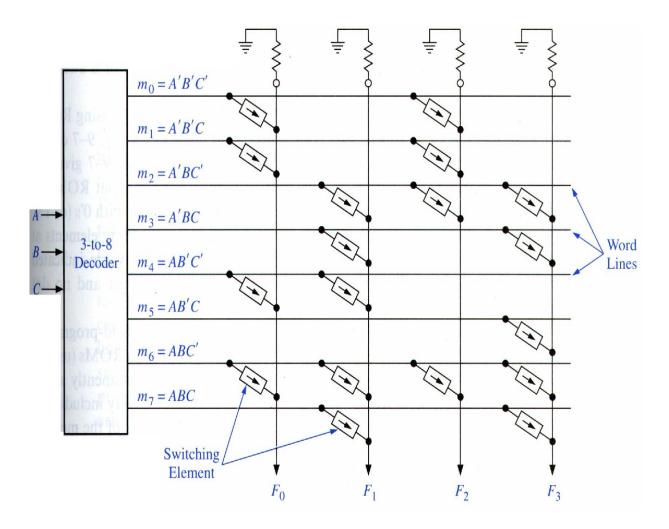

#### **ROM Basic Structure**

• 8-word x 4 bit ROM

$- F_0 = m_0 + m_1 + m_4 + m_6$

## Multiple-Output Network Using ROM

• BCD to Excess-3 code

| a | b | С | d |   | w | x | y | Z |

|---|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 3 | 0 | 0 | 1 | 1 |

| 0 | 0 | 0 | 1 |   | 0 | 1 | 0 | 0 |

| 0 | 0 | 1 | 0 |   | 0 | 1 | 0 | 1 |

| 0 | 0 | 1 | 1 |   | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 0 |   | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 |   | 1 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |   | 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 1 |   | 1 | 0 | 1 | 0 |

| 1 | 0 | 0 | 0 |   | 1 | 0 | 1 | 1 |

| 1 | 0 | 0 | 1 |   | 1 | 1 | 0 | 0 |

| - |   |   |   |   |   |   |   |   |

## Types of ROM

- Mask-programmable ROM

- Contents are stored during fabrication.

- Field-programmable ROM

- PROM: programmable ROM

- Fusible link (PROM programmer)

- EPROM: erasable PROM

- Use ultraviolet light for erasure.

- EEPROM: electrically erasable

PROM.

- Flash memory

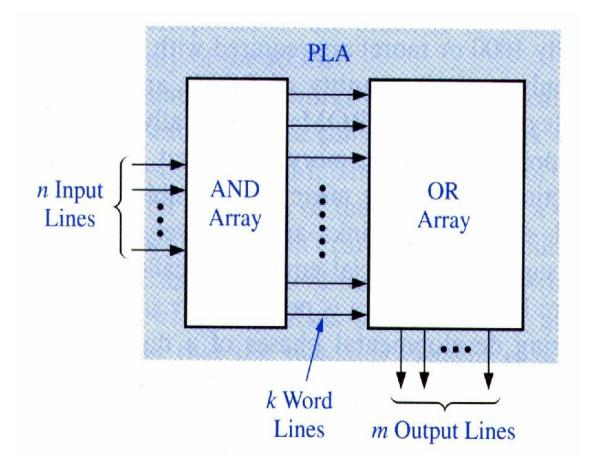

#### Programmable Logic Devices

- PLA (programmable logic array)

- Realize m functions of n variables.

# Implementation procedure for PLA

- Prepare the truth table based on your system

- Write the Boolean expression in SOP (sum of product) form.

- Obtain the minimum SOP form to reduce the number of product terms to a minimum.

- Decide the input connection of the AND matrix for generating the required product term.

- Then decide the input connections of OR matrix to generate the sum terms.

- Decide the connections of invert matrix.

- Program the PLA.

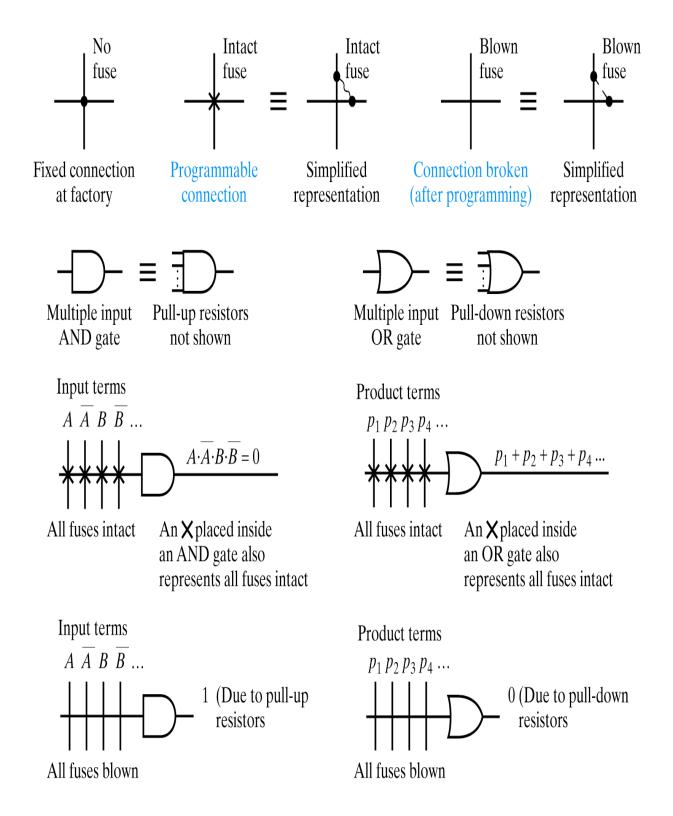

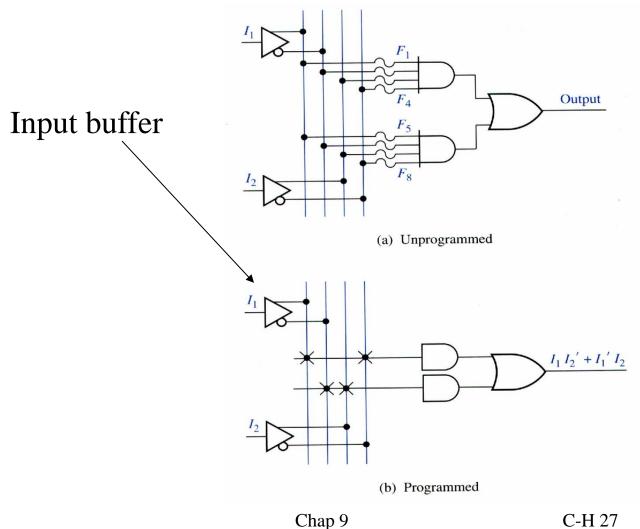

#### Programmable Symbology

**Figure 3.6.2** Programmable symbology summary for the different types of PLDs.

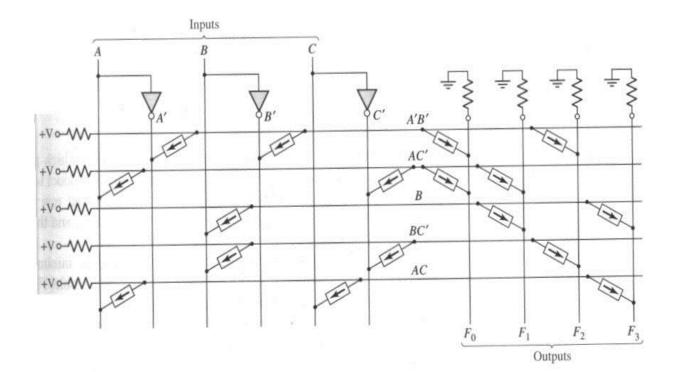

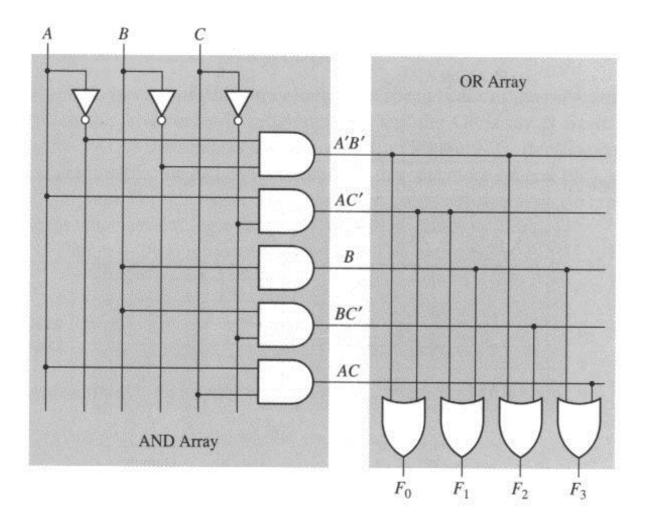

#### PLA

• PLA 3 inputs, 5 product terms, 4 outputs.

| Product                       | Inputs                                               | Outputs                                              | $F_0 = A'B' + AC'$                                      |

|-------------------------------|------------------------------------------------------|------------------------------------------------------|---------------------------------------------------------|

| Term                          | A B C                                                | $F_0$ $F_1$ $F_2$ $F_3$                              |                                                         |

| A'B'<br>AC'<br>B<br>BC'<br>AC | $\begin{array}{rrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrr$ | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ | $F_{1} = AC' + B$ $F_{2} = A'B' + BC'$ $F_{3} = B + AC$ |

#### PLA

Inputs

#### • PLA circuit

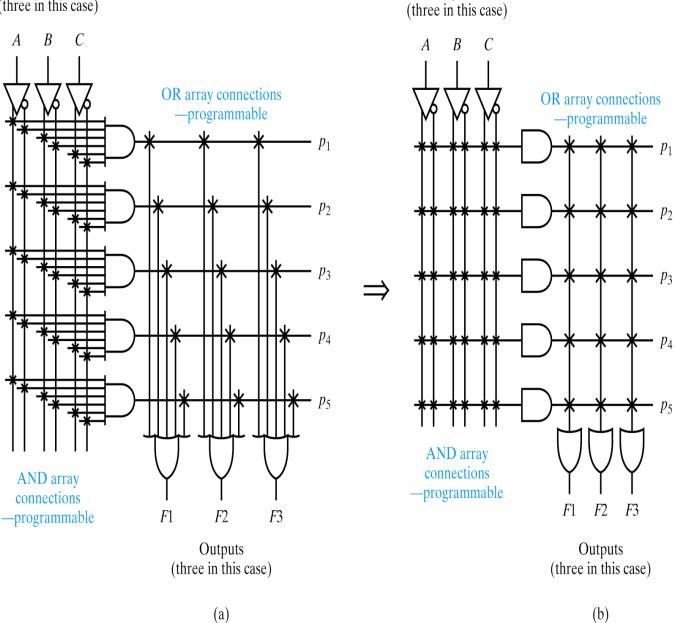

Inputs (three in this case)

**Figure 3.6.4** PLA circuit: (a) circuit representation using gates, (b) simplified circuit representation using gates.

#### PLA (cont.)

• PLA 3 inputs, 5 product terms, 4 outputs. AND-OR array.

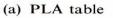

#### PLA Application

- $f_1 = a'bd + abd + ab'c' + b'c$

- $f_2 = c + a'bd$

- $f_3 = bc + ab'c' + abd$

- If abcd = 0111, 1st, 5th, 6th rows are selected.  $f_1 = 1 + 0 + 0$ ,  $f_2 = 1 + 1 + 0$ , etc.

| a b c d         | $f_1 f_2 f_3$ |

|-----------------|---------------|

| $0 \ 1 \ - \ 1$ | 1 1 0         |

| $1 \ 1 \ - \ 1$ | 1 0 1         |

| $1 \ 0 \ 0 -$   | 1 0 1         |

| -01-            | 1 0 0         |

| 1 -             | 0 1 0         |

| -11 -           | 0 0 1         |

(b) PLA structure

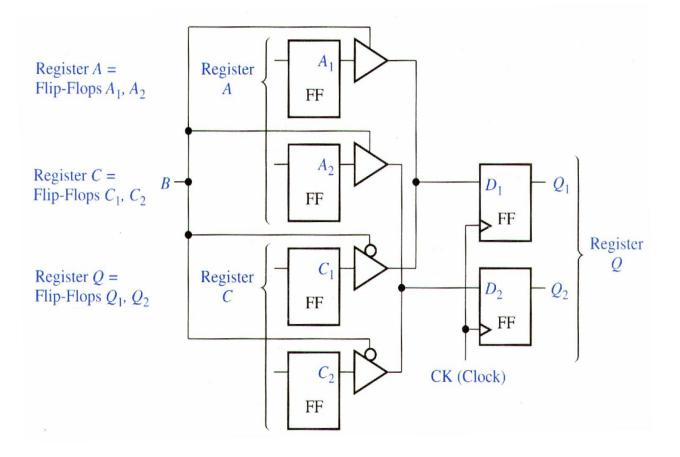

# Programmable Array Logic (PAL)

- AND array is programmable. OR array is fixed.

- Use input buffer to drive many ANDs.

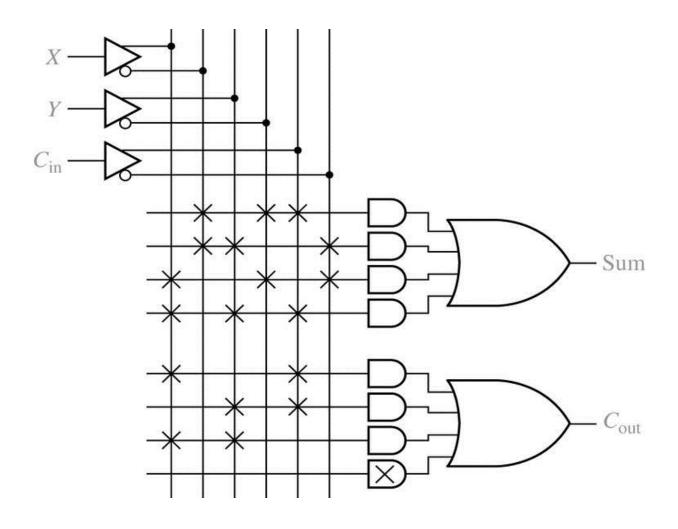

# Programmable Array Logic (PAL)

• Full Adder using a PAL

# Why prefers PLA rather than ROM

- A combinational circuit may occasionally have don't-care conditions. When implemented with a ROM, a don't care condition becomes an address input that will never occur.

- The words at the don't care address need not be programmed and may be left in their original state(all 0's or all 1's ).

- The has the result that all the bit patterns available in ROM are used, but for the don't care addresses you really can do without them.

#### What Programmable Means

- "programmable" does not indicate that all PLAs are field-programmable.

- Many are mask-programmed during manufacture in the same manner as a mask ROM.

- This is particularly true of PLAs that are embedded in more complex and numerous integrated circuits such as microprocessors.

- PLAs that can be programmed after manufacture are called FPGA (Fieldprogrammable gate array)

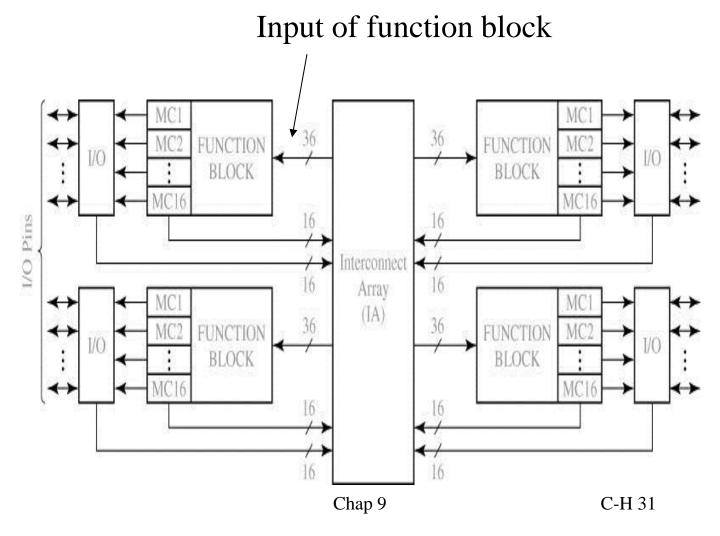

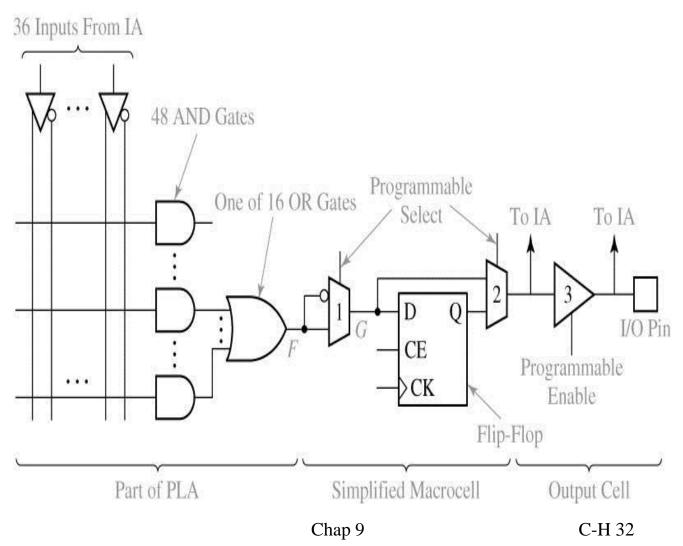

# Complex Programming Logic Devices

- Xilinx XCR3064XL CPLD

- Function block (16 macrocells)= PLA

- Macrocell = a flip flop + multiplexers

- IA routes signals

#### Function Block and MC

- Signal from PLA -> marcocell -> I/O pin

- Use CAD tool to fit the design into the PLD.

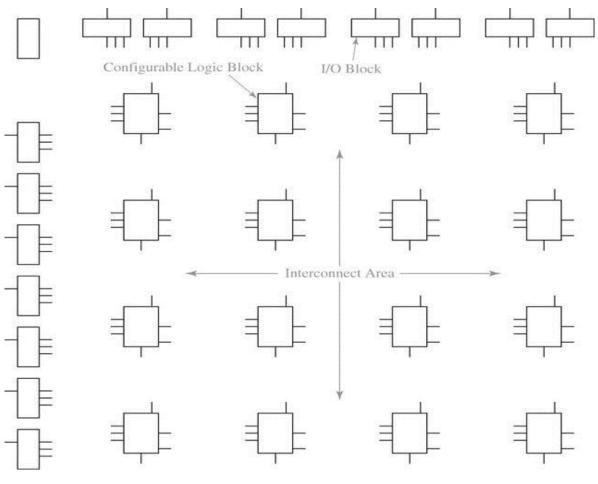

# Field Programmable Gate Arrays (FPGA)

- Logic cell: configurable logic blocks (CLBs)

- Input/Output blocks (I/O blocks)

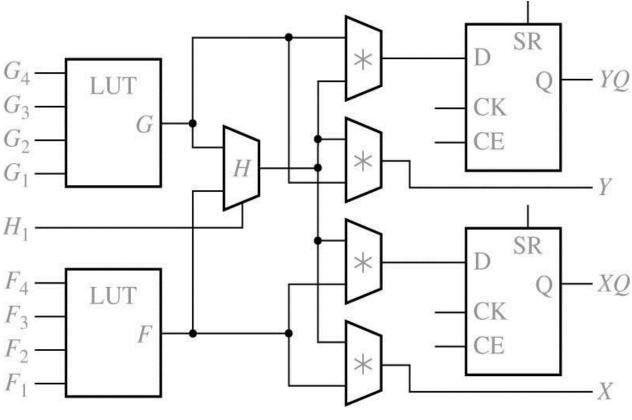

# Configurable Logic Block

- Inside a CLB: function generators (LUT), FFs, and MUXs

- LUT: lookup table (truth table) is a reprogrammable ROM (16 1-bit words)

\*= Programmable MUX

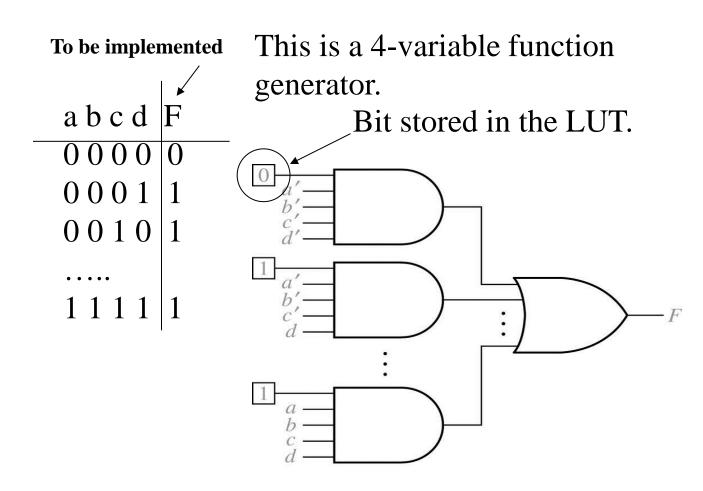

## A Lookup Table (LUT)

- If we want F = abc (one minterm) - 1110 (and F=1) + 1111 (and F=1)

- Or if we want F = a'b'c'd' + a'b'cd' + ...abcd.

(15 minterms)

- Require a single function generator. Program the LUT table to get what we want.

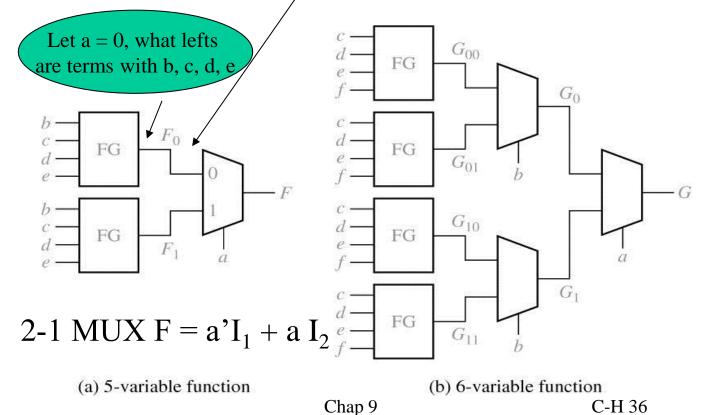

#### Shannon's Expansion Theorem

• What if # of variables > 4 variables

$$f(x_1, x_2, \dots, x_n) = x_i' f(x_1, x_2, \dots, x_{i-1}, 0, x_{i+1}, \dots, x_n) + x_i f(x_1, x_2, \dots, x_{i-1}, 1, x_{i+1}, \dots, x_n) = x_i' f_0 + x_i f_1$$

f(a, b, c, d, e) = a' f(0, b, c, d, e) + a f(1, b, c, d, e)