### Handout: Volatile and Non-volatile Memories

## **Charge-Based Non-volatile RAM**

#### NAND flash

NOR flash

#### What's up? -> What was up in 1967?

#### SOLID-STATE DEVICE RESEARCH CONFERENCE

- 6) Interface Properties of Thin-Film Al-Al<sub>2</sub>O<sub>3</sub>-CdSe Transistors—A. Waxman, RCA Laboratories.

- 7) A Floating Gate and Its Application to Memory Devices—K. Kahng and S. M. Sze, Bell Telephone Laboratories, Inc.

#### SESSION II—HIGH FRE-QUENCY BULK EFFECTS

Chairman: C. Hilsum Organizer: M. A. Lampert

1) Epitaxial Gallium Arsenide for Gunn-Effect Oscillators—C. M. Wolfe, A. G. Foyt, and W. T. Lindley, M.I.T. Lincoln Laboratory. The year is 1967, In IEEE Transactions on Electron Devices

#### Principle of operation...how much do you "charge"?

#### Floating-gate transistor

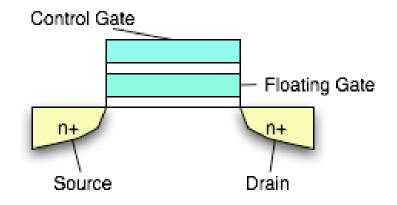

- A flash memory cell resembles a standard MOSFET, except the transistor has two gates instead of one.

- On top is the control gate (CG), as in other MOS transistors, but below this there is a floating gate (FG) insulated all around by an oxide layer.

- Because the FG is electrically isolated by its insulating layer, any electrons placed on it are trapped there and, under normal conditions, will not discharge for many years. When the FG holds a charge, it screens (partially cancels) the electric field from the CG, which modifies the threshold voltage (V<sub>T</sub>) of the cell.

- During read-out, a voltage intermediate between the possible threshold voltages is applied to the CG, and the MOSFET channel will become conducting or remain insulating, depending on the V<sub>T</sub> of the cell, which is in turn controlled by charge on the FG. The current flow through the MOSFET channel is sensed.

- In a multi-level cell device, which stores more than one bit per cell, the amount of current flow is sensed (rather than simply its presence or absence), in order to determine more precisely the level of charge on the FG.

**Dr. Simon M. Sze** coinvented of the nonvolatile semiconductor memory (NVSM) which has subsequently given rise to a large family of memory devices including the

Flash memory and the EEPROM.

#### **Technological origin of flash memory**

- Floating gate transistor : Dawon Kahng and Simon Sze, Bell lab, 1967.

- Flash: Dr. Fujio Masuoka, Toshiba, 1980.

- Adding erase gate to floating gate transistor

- Toshiba announced NAND flash at the 1987.

- Intel put into work, first NOR flash in 1988

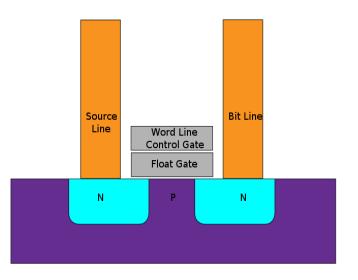

## **NAND Flash**

NAND Flash advantages are faster block erase time and write time. But very slow in random reads

- Since the bit line discharge path goes through multiple series transistors, the time discharge the bit line (the time to read the selected bit) will be much longer than that of the NOR.

- NAND is best for sequential accesses such as data storage

- NAND's silicon per bit is only about 40% of that for NOR.

# **NOR Flash**

- NOR Flash advantages are its random-access and bytewrite capabilities.

- NOR Flash allows the retrieval of data as small as a single byte. NOR Flash excels in applications where data is randomly retrieved or written.

- NOR is most often found built into cellular phones (to store the phone's operating system) and PDAs and is also used in computers to store the BIOS program that runs to provide the start-up functionality.

- Fast read operations, but slow in write and erase operations.

# **Multi-Level Cell: MLC**

- MLC devices use a special type of cell that stores 2 bits per cell, compared with traditional single-level cell (SLC) devices, which can store only 1 bit per cell.

- Impact on programming and reading times?

- Readout of a sense amplifier? Threshold voltages?

- MLC technology offers obvious density advantages. However, MLC lacks the speed and reliability of its SLC counterpart.

- For this reason, SLC devices are used in the majority of high-performance and high-endurance applications; MLC devices are typically used in consumer and other low-cost products

### What's new?

Phase change memory

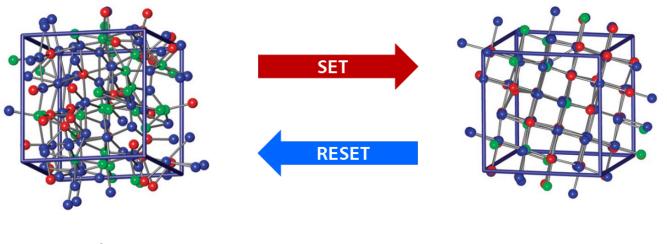

# States of phase change memory

PCM

Use material property to store information, two states: crystalline and amorphous

Amorphous High resistivity Logic H

Crystalline Low resistivity Logic L

### PCM made of ....

- ◆ Chalcogenide-based alloy (Ge, Sb, and Te or GST); /kælkədʒɨn/ (硫族元素 氧、硫、硒、碲的總稱

- First exploited by Stanford Ovshinsky in the 60s

- Gordon Moore did lots of study in the 70s

- A recent renewed interest

- Intel + Ovonyx + STMicro joint effort in 2003

- 2007, Intel and ST formed a new venture Numonyx

- Numonyx was acquired by Micron 2010

- Samsung shipped the first 512Mb PCM chip in April, 2010

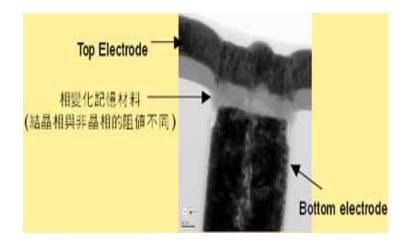

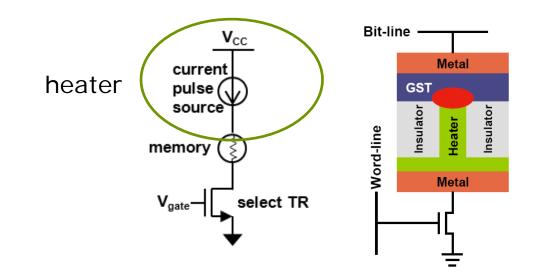

# Physics of state change

#### High pulse current -> heat

PCM的記憶體晶胞使用相變化 材料(通常是Chalcogenide材 料,現有多種材料被研究)作 為記憶單元,此種材料具有適 當的晶相轉換溫度,在控制加 熱參數與散熱條件之下,可以 改變材料的結晶狀態而衍生不 同的電阻值,藉此可以用來記 錄0或1的訊號。

PCM memory cell

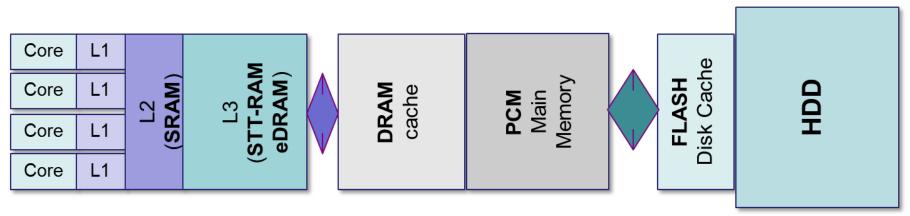

# Volatile and Non-volatile RAMs

#### PCM v.s. some of the rest

| Memory Type                 | DRAM           | 6T SRAM             | NOR FLASH           | PCM                                   | MRAM              | STT-RAM                                | FeRAM                              | Memristor          |

|-----------------------------|----------------|---------------------|---------------------|---------------------------------------|-------------------|----------------------------------------|------------------------------------|--------------------|

| Volatility                  | Volatile       | Volatile            | NVM                 | NVM                                   | NVM               | NVM                                    | NVM                                | NVM                |

| Cell Size (F <sup>2</sup> ) | 6-12           | 50 - 80             | 7 - 11              | 5-8                                   | 16-40             | 6-20                                   | Large                              | scalable           |

| Read                        | Destructive    | Partial Destructive | Non-Destructive     | Non-Destructive                       | Non-Destructive   | Non-Destructive                        | Destructive                        | Non-Destructive    |

| Erase Granularity           | Direct         | Direct              | Block               | Direct                                | Direct            | Direct                                 | Direct                             | Direct             |

| Write/Erase/Read Time       | 50ns/50ns/50ns | 8ns/8ns/8ns         | 1µs/1-100ms/60ns    | 10ns/50ns/20ns                        | 30ns/30ns/30ns    | 20ns/20ns/20ns                         | 80ns/80ns/80ns                     | ??                 |

| Programming Energy          | Medium         | Medium              | High                | Medium                                | Medium            | Low                                    | Medium                             | Low?               |

| Write/Read Endurance        | ~~0/~~00       | ~∞/~∞               | 10 <sup>6</sup> /~∞ | 10 <sup>8</sup> ~10 <sup>12</sup> /~∞ | $10^{12}/10^{12}$ | 10 <sup>15</sup> /10 <sup>15</sup> (?) | 10 <sup>12</sup> /10 <sup>12</sup> | 10 <sup>7</sup> /? |

| Multi-Level Cell            | No             | No                  | Yes                 | Yes                                   | stacking          | stacking                               | No                                 | stacking           |

| Cost per bit                | Low            | High                | Medium              | Low                                   | ??                | ??                                     | High                               | ??                 |

| Supply Voltage              | 3V             | <1V                 | 6-8V                | 1.5-3V                                | 3V                | <1.5V                                  | 2-3V                               | <1.5V?             |

#### SST-RAM: Spin-transfer torque RAM

# **Repair flash memory**

#### High heat helps 'heal' flash memory chips (BBC news, Dec. 2012)

- A brief jolt of 800C heat can stop flash memory wearing out, researchers in Taiwan have found.

- Flash memory is widely used in computers and electronic gadgets because it is fast and remembers data written to it even when unpowered.

- However, flash memory reliability suffers significantly after about 10,000 write and read cycles.

- Using heat, the researchers have found a way to "heal" flash memory materials to make them last 100 million cycles.

- Hot chip Heat has long been known to help heal degraded materials in old flash memory. But because the heat healing process

meant baking the memory chip in an oven at 250C for hours, few saw it as a practical solution.

- Researchers at electronics company Macronix have found a way around this by re-designing chips to put a heater alongside the memory material that holds the data.

- In a paper due to be presented at the International Electron Devices Meeting 2012, the Macronix researchers said their onboard heater applied a jolt of heat to small groups of memory cells. Briefly heating those locations to about 800C returned damaged memory locations to full working order.

- The re-designed memory chip was safe, they said, because very small areas were being heated for only a few milliseconds. The process also consumed small amounts of power so should not significantly reduce battery life on portable gadgets, they said.

- Tests carried out by Macronix on the novel memory chips shows that they can last at least 100 million write and read cycles. The true upper limit of their reliability has not been plumbed, the researchers told IEEE Spectrum, because it takes weeks to write and read data tens of millions of times, even to fast memory chips. Testing for billions of cycles would take "months", said the researchers.

## Non-volatile circuit

- Combinational circuit

- Sequential circuit

- Back up registers before shutdown

What if all registers are backed up by a nearby NV-RAM?